# GHDL, What's new ? Tristan Gingold

- What is GHDL ?

- Improvements since FOSDEM'15

- Multi language simulation Proof of concept

# What is GHDL?

# What is GHDL ?

If you have missed last year presentation:

- Free, open-source VHDL simulator

- Generate object code (with gcc, LLVM or it's generator)

- Support VHDL 1987 till 2008

- github.com/tgingold/ghdl

# What is GHDL ?

- Command line tool (no IDE)

- Generate VCD, GHW or FST waveforms

- GTKwave compatible

- VHPI and VPI support

- Partial support of PSL

# Typical use cases

- FOSS activist: use a free tool

- Nightly testing

- Coverage (with gcov)

#### What's new ?

# What's new ?

- Switch to git

- Move to github

- Docs on ghdl.readthedocs.org

- Continuous integration on <u>travis-ci.org</u>

### GHDL 0.33 released

- For Linux x86, x86-64

- generic, debian and Ubuntu

- For Mac OS X

- For Windows

- First version with good VHDL 2008 support

## New features

- More VHDL 2008 features

- Many bugs fixed

- Support of VUnit

- OSS unit testing framework

- Support of OSVVM

- Open Source VHDL Verification Methodology

### Post release features

- Mcode for x86-64:

- Mcode is builtin code generator

- Code generation is much faster than IIvm or gcc

- Scale very well

- Easy to build (no dependencies)

- Was i386 + fpu only

- Now i386 or x86-64 + SSE2

#### Post release features

- Optimizations

- Better handling of signals

- Explicit process state

# Future work

- More optimisations

- Multi language simulation

- Synthesis ?

# Multi language simulation

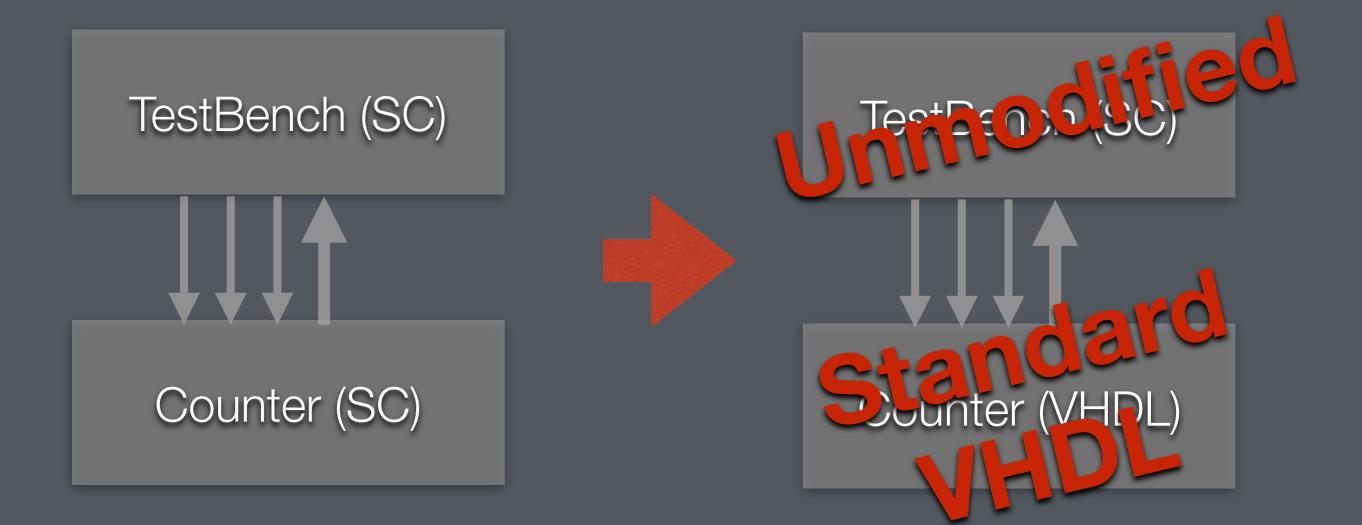

# VHDL + SystemC

- Purpose: simulate both VHDL and SystemC

- Using GHDL

# Why SystemC ?

- And not Verilog ?

- SystemC is simpler

- Simulation cycle is like VHDL

- Use the same compilation model as GHDL

- Object files

- Final link

# Proof of Concept

### Proof of concept: constraints

- Main is SystemC

- No change in test bench or VHDL code

- No change in SystemC kernel

#### Proof of concept: simplifications

- Only one VHDL module

- Multi-language semantic weakly defined

- Can change GHDL code

## Proof of Concept

| <pre>SC_MODULE (first_counter) {</pre>                                                           |         |                                                     |

|--------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------|

| sc_in_clk                                                                                        | _       | // Clock input of the design                        |

|                                                                                                  | •       |                                                     |

| <pre>sc_in<bool></bool></pre>                                                                    | reset ; | <pre>// active high, synchronous Reset input</pre>  |

| <pre>sc_in<bool></bool></pre>                                                                    | enable; | <pre>// Active high enable signal for counter</pre> |

| <pre>sc_out<sc_uint<4> &gt; counter_out; // 4 bit vector output of the counter</sc_uint<4></pre> |         |                                                     |

```

entity counter is

port (clk : bit;

reset : bit;

enable : bit;

counter_out : out bit_vector (3 downto 0));

end counter;

```

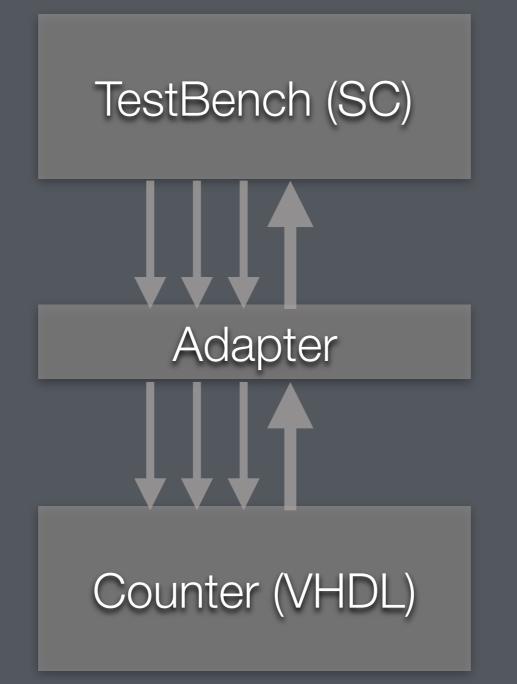

# Proof of Concept: Adapter

- Initialize GHDL simulator

- Instantiate the VHDL blocks

- Convert values between SystemC and VHDL

# GHDL initialization

```

SC_CTOR(first_counter) {

// Elaborate instance.

grt_init (); // Elab Ada code

grt_main_init (sc_argv()[0], sc_argc (), sc_argv()); // Init grt

```

```

void end_of_elaboration () {

//cout << "end of elab" << endl;

__ghdl_simulation_init ();

}</pre>

```

# VHDL instantiation

```

grt_main_elab (); // Elaborate vhdl unit

instance = (struct counter_INSTTYPE *) __ghdl_rti_top_instance;

```

struct counter\_INSTTYPE {

struct ghdl\_entity\_link RTI;

```

struct ghdl_signal *clk_SIG;

std__standard__bit *clk_VALP;

```

struct ghdl\_signal \*reset\_SIG;

std\_\_standard\_\_bit \*reset\_VALP;

struct ghdl\_signal \*enable\_SIG;

std\_\_standard\_\_bit \*enable\_VALP;

struct ghdl\_signal \*counter\_out\_SIG[4];

std\_\_standard\_\_bit \*counter\_out\_VALP;

C representation of the VHDL entity, as compiled by GHDL

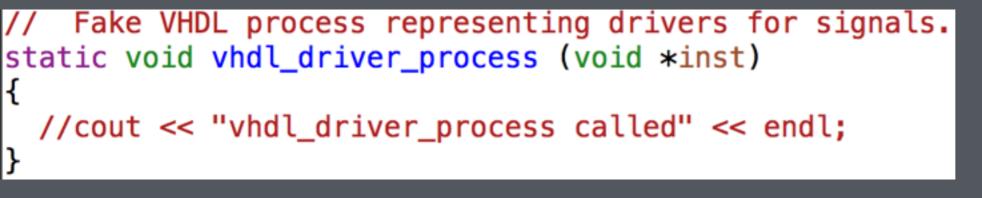

// Register an external process and add drivers for inputs

driver\_proc = \_\_ghdl\_register\_foreign\_process (this, &vhdl\_driver\_process);

\_\_ghdl\_process\_add\_driver (instance->clk\_SIG);

\_\_ghdl\_process\_add\_driver (instance->reset\_SIG);

\_\_ghdl\_process\_add\_driver (instance->enable\_SIG);

# Value Conversions: input

sc\_in<bool>

enable;

// Active high enable signal for counter

#### void enable\_adapt (void) { //cout << "enable event: " << enable << endl;</pre> \_ghdl\_set\_current\_process (driver\_proc); ghdl\_signal\_simple\_assign\_e8 (instance->enable\_SIG, enable); vhdl\_cycle\_ev.notify(SC\_ZER0\_TIME); }

#### Ask SystemC to run GHDL kernel

SC\_METHOD(enable\_adapt); sensitive << enable;</pre>

So if an input change, it is propagated to VHDL

# Kernel interleaving

sc\_event vhdl\_cycle\_ev;

void vhdl\_cycle (void) {

//cout << "vhdl cycle" << endl;

if (\_\_ghdl\_simulation\_step () == 0)

vhdl\_cycle\_ev.notify(SC\_ZER0\_TIME);</pre>

SC\_METHOD(vhdl\_cycle);

sensitive << vhdl\_cycle\_ev;</pre>

Need a new delta cycle

So VHDL kernel is run in case of event

# Value Conversions: Output

// Register an external process and add sensitivity for outputs

\_\_ghdl\_register\_foreign\_process (this, &vhdl\_counter\_driver\_process);

for (int i = 0; i < 4; i++)</pre>

\_\_\_ghdl\_process\_add\_sensitivity (instance->counter\_out\_SIG[i]);

```

static void vhdl_counter_driver_process (void *inst)

{

first_counter *fc = static_cast<first_counter *>(inst);

fc->counter_adapt ();

}

```

#### So if a VHDL signal change, a method is called

# Value Conversions: Output

sc\_out<sc\_uint<4> > counter\_out; // 4 bit vector output of the counter

```

void counter_adapt (void) {

struct counter_INSTTYPE *inst = instance;

unsigned int v = 0;

for (int i = 0; i < 4; i++)

v = (v << 1) | inst->counter_out_VALP[i];

//cout << "counter event: " << v << endl;

counter_out = v;

}</pre>

```

#### Convert from a VHDL signal to a SystemC signal

#### Proof of concept: Conclusions

- Just of Proof of Concept but:

- It works!

- required only changes in GHDL runtime (kernel)

- need to split the simulation loop

### Proof of concept: Future

- Generate the adapter automatically

- Mapping is not obvious

- Avoid delta-cycles between SC and VHDL

- Need to modify SystemC kernel

- Multiple VHDL instances

- Instantiation of SC by VHDL blocks