open source FPGA toolchain and hardware

enabling innovative FPGA solutions

- Track: Embedded, Mobile and Automotive devroom

- Room: UD2.120 (Chavanne)

- Day: Saturday

- Start: 12:30

- End: 12:55

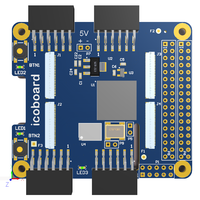

We will bring a fully open source FPGA toolchain for the RaspberryPi FPGA board we developed.

The board can be seen in action at https://twitter.com/oe1cxw/status/673484838037516288

We do have a working open source toolchain for Lattice FPGAs. We can generate a bitstream on a RaspberryPi or on any other CPU.

We will make available some of our Lattice FPGA boards for the RaspberryPi to qualified FPGA hackers and demonstrate also cool demos with lots of LEDs.

Currently Clifford did port a 32bit Risc-V CPU to the FPGA, and can run software on the Risc-V CPU. It is also planned to port micropython to the board.

Yosys (Yosys Open Synthesis Suite) is an Open Source Verilog synthesis and verification tool.

Project IceStorm aims at reverse engineering and documenting the bit-stream format of Lattice iCE40 FPGAs and providing simple tools for analyzing and creating bit-stream files, including a tool that converts iCE40 bit-stream files into behavioral Verilog. Currently the bitstream format for iCE40 HX1K and HX8K is fully documented and supported by the tools.

Arachne-PNR is an Open Source place&route tool for iCE40 FPGAs based on the databases provided by Project IceStorm. It converts BLIF files into an ASCII file format that can be turned into a bit-stream by IceStorm tools.

This three projects together implement a complete open source tool-chain for iCE40 FPGAs. It is available now and it is feature complete (with the exception of timing analysis, which is work in progress).

Speakers

| Edmund Humenberger |