Understanding JESD204B

High-speed inter-device data transfers for SDR

- Track: Software Defined Radio devroom

- Room: AW1.120

- Day: Saturday

- Start: 13:30

- End: 14:00

JESD204B is a industry standard for interfacing high-speed converters (ADC, DAC) to logic devices (FPGA, ASIC). This presentation will give a introduction to the JESD204B standard which is gaining increasing adoption in SDR solutions to connect the RF-fronted device to the processing device.

JESD204B is a industry standard for interfacing high-speed converters (ADC, DAC) to logic devices (FPGA, ASIC).

Software-defined-radio solutions follow a trend of ever increasing channel bandwidth and diversity (e.g. MIMO). Another trend is the transition from zero-IF to direct-IF, which bypasses the analog modulator and samples the full spectrum up to the desired signal. Both of them require additional data throughput rates which can reach the limits of more traditional interfaces like CMOS or LVDS. The JESD204B standard has been designed to overcome these restrictions and allow higher throughput data rates between the converter and the logic device. It is as such not surprising that to accommodate the increased data rate demands of such solutions JESD204B is often adopted, both for discrete as well as integrated RF designs.

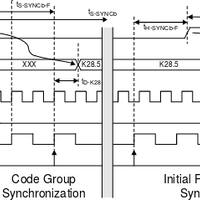

In addition to specifying the physical layer the JESD204B specification also has a protocol layer defining data mapping and encoding as well as standard methods for commonly needed features like data integrity checks, multi-chip synchronization and deterministic latency.

This presentation will provide an introduction to the JESD204B standard in the context of software-defined-radio explaining how the different layers inside the JESD204B standard interact, giving developers a understanding of how to setup and configure a JESD204B system.

Speakers

| Lars-Peter Clausen |