# Building Loosely-coupled RISC-V Accelerators

Using Chisel/FIRRTL to build accelerator templates and collateral for the ESP SoC platform

Schuyler Eldridge

2020-02-01

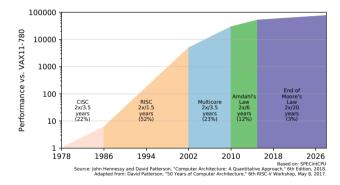

# The Golden Age of Computer Architecture is about Accelerators (Assuming you don't hit the Accelerator Wall...<sup>1</sup>)

Figure 1: 50 Years of Process Performance (Measured as SPECInt Score)

<sup>1</sup>Fuchs, A. and Wentzlaff, D., *The accelerator wall: Limits of chip specialization*, 2019

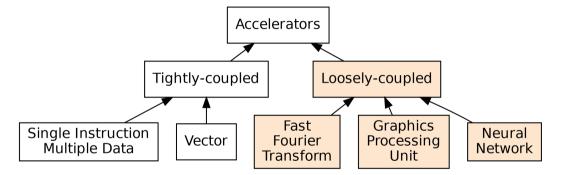

Figure 2: A type hierarchy of accelerators

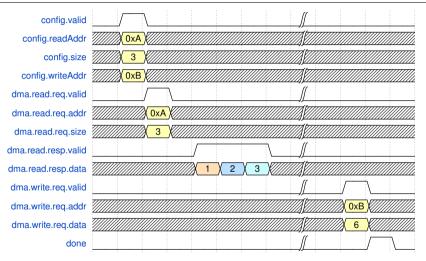

### Loosely-coupled: Config, Read, Compute, Write

Figure 3: Waveform showing loosely-coupled accelerator timing<sup>2</sup>

<sup>2</sup>Waveform generated using using Wavedrom (github.com/wavedrom/wavedrom)

- Bring your own accelerator in any language

- Accelerator can be easily integrated with a Leon3 or Ariane System-on-Chip

- Bring your own accelerator in any language

- Accelerator can be easily integrated with a Leon3 or Ariane System-on-Chip

### Clarifications

- Bring your own accelerator in any language

- Accelerator can be easily integrated with a Leon3 or Ariane System-on-Chip

### Clarifications

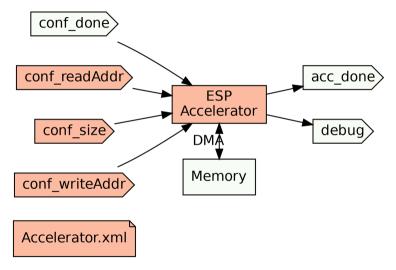

How is ESP made aware of the accelerator? (An XML file)

- Bring your own accelerator in any language

- Accelerator can be easily integrated with a Leon3 or Ariane System-on-Chip

### Clarifications

- How is ESP made aware of the accelerator? (An XML file)

- How does the user know what to write? (An example module)

Figure 4: ESP Accelerator Socket

<sup>3</sup>Taylor, M.B., *Basejump stl: Systemverilog needs a standard template library for hardware design*, 2018

SystemVerilog is hard to use to build libraries.<sup>3</sup>

<sup>3</sup>Taylor, M.B., *Basejump stl: Systemverilog needs a standard template library for hardware design*, 2018

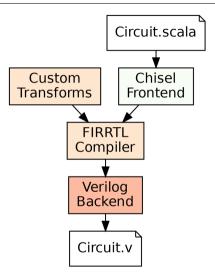

- Chisel is a Scala hardware DSL

- FIRRTL is a circuit IR and an optimizing circuit compiler

Chisel is a Scala hardware DSL

FIRRTL is a circuit IR and an optimizing circuit compiler

- Chisel is a Scala hardware DSL

FIRRTL is a circuit IR and an antimizing circuit compiler

- optimizing circuit compiler

### Language Power

1 Parametric

Chisel is a Scala hardware DSL

FIRRTL is a circuit IR and an optimizing circuit compiler

- 1 Parametric

- 1 Parametric Polymorphic

- Chisel is a Scala hardware DSL

FIRRTL is a circuit IR and an

- optimizing circuit compiler

- 1 Parametric

- 1 Parametric Polymorphic

- First Class Functions

Chisel is a Scala hardware DSL

FIRRTL is a circuit IR and an optimizing circuit compiler

- 1 Parametric

- **1** Parametric Polymorphic

- First Class Functions

- Functional Programming

**IBM**

- Chisel is a Scala hardware DSL

FIRRTL is a circuit IR and an

- optimizing circuit compiler

- 1 Parametric

- 1 Parametric Polymorphic

- First Class Functions

- Functional Programming

- Object-oriented Programming

Chisel is a Scala hardware DSL

FIRRTL is a circuit IR and an optimizing circuit compiler

#### Language Power

- 1 Parametric

- 1 Parametric Polymorphic

- First Class Functions

- Functional Programming

- Object-oriented Programming

Figure 5: Chisel/FIRRTL Verilog compilation

### chisel-lang.org

Chisel3 Testers ChiselTest FIRRTL Treadle Diagrammer Community

Figure 6: Chisel Website

Schuyler Eldridge - Building Loosely-coupled RISC-V Accelerators

```

trait Specification {

/** Accelerator Config */

def config: Config

}

```

```

abstract class Implementation

extends Module

with Specification {

```

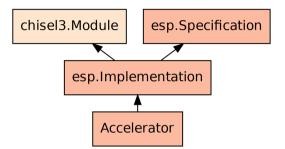

Figure 7: Composition of an ESP accelerator

```

/** Accelerator Name */

def implementationName: String

}

```

An ESP accelerator is composed of an Implementation and a Specification.

<sup>4</sup>github.com/IBM/esp-chisel-accelerators

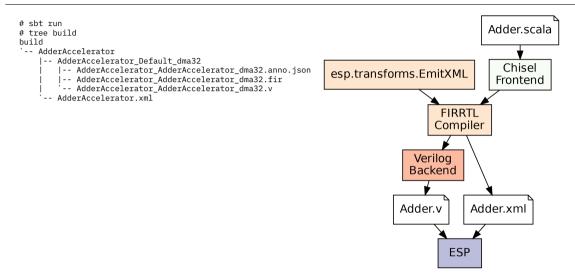

#### trait AdderSpec extends Specification {

```

override lazy val config = Config(

name = "AdderAccelerator".

description = "Reduces a vector via addition",

memorvFootprintMiB = 1.

deviceId = O \times F.

param = Arrav(

Parameter( name = "readAddr" ).

Parameter( name = "size" ),

Parameter( name = "writeAddr" )

```

ş

### class Adder extends Implementation with AdderSpec {

#### override val implementationName = "AdderAccelerator"

```

/** Implement me! */

}

```

### **Canned Demo**

Figure 8: ESP Chisel Accelerators Flow

#### <sld>

#### <sup>5</sup>https://github.com/grebe/ofdm

### Current esp-chisel-accelerators

- CounterAccelerator ("hello world")

- AdderAccelerator

- FFTAccelerator<sup>5</sup>

<sup>&</sup>lt;sup>5</sup>https://github.com/grebe/ofdm

### Current esp-chisel-accelerators

- CounterAccelerator ("hello world")

- AdderAccelerator

- FFTAccelerator<sup>5</sup>

### **Future Work**

- Additional collateral generation including:

- Basic bare metal and Linux test programs

- Drivers

- New accelerators

<sup>&</sup>lt;sup>5</sup>https://github.com/grebe/ofdm

### More Info

| ESP     | github.com/sld-columbia/esp            |

|---------|----------------------------------------|

|         | github.com/IBM/esp-chisel-accelerators |

| Chisel3 | github.com/freechipsproject/chisel3    |

| Twitter | @chisel_lang                           |

| FIRRTL  | github.com/freechipsproject/firrtl     |

Figure 9: github:@seldridge

The research reported in this talk was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the authors and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. government.

Distribution Statement A: Approved for public release, distribution unlimited.