# Open ESP The Heterogeneous Open-Source Platform for Developing RISC-V Systems Luca P. Carloni with Davide Giri

FOSDEM' 20, Brussels Feb 1, 2020

#### **Open Source Release of ESP**

0 9 0 🖵

#### The ESP Vision

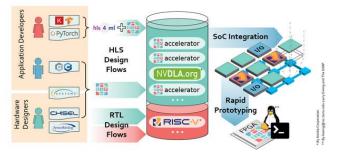

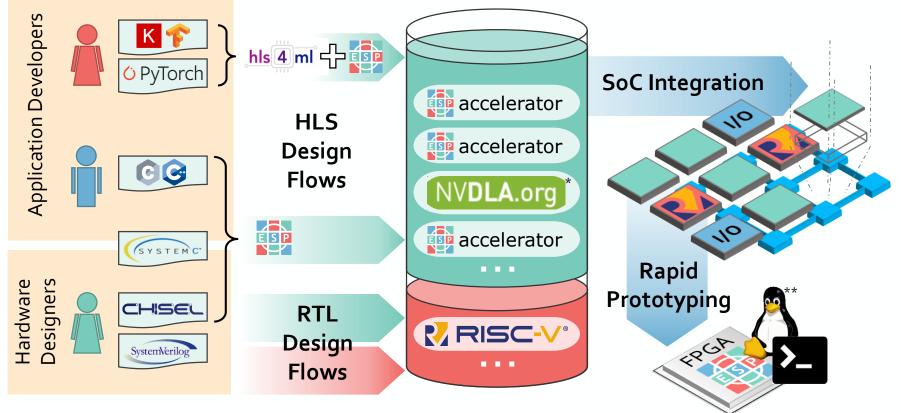

ESP is an open-source research platform for heterogeneous system-on-chip design that combines a flexible tile-based architecture and a modular system-level design methodology.

ESP provides three accelerator flows: RTL, high-level synthesis (HLS), machine learning frameworks. All three design flows converge to the ESP automated SoC integration flow that generates the necessary hardware and software interfaces to rapidly enable full-system prototyping on FPGA.

#### Overview

Latest Posts

Video proceedings of the ESP talk at the RISC-V Summit

The video of the ESP talk at the RISC-V summit 2019 is now available on Youtube.

Read more

Published: Jan 25, 2020

Two accepted talks at FOSDEM 2020 in Brussels

We will give two talks in the RISC-V developer room at FOSDEM in Brussels (Beloium) on February 1st.

#### https://www.esp.cs.columbia.edu

# Why ESP?

Heterogeneous systems are pervasive Integrating accelerators into a SoC is hard Doing so in a scalable way is very hard

Keeping the system simple to program while doing so is even harder

**ESP** makes it easy

ESP combines a scalable architecture with a flexible methodology ESP enables several accelerator design flows and takes care of the hardware and software integration

#### ESP Vision: Domain Experts Can Design SoCs

COLUMBIA UNIVERSITY IN THE CITY OF NEW YORK \* By Nvidia Corporation \*\* By lewing@isc.tamu.edu Larry Ewing and The GIMP

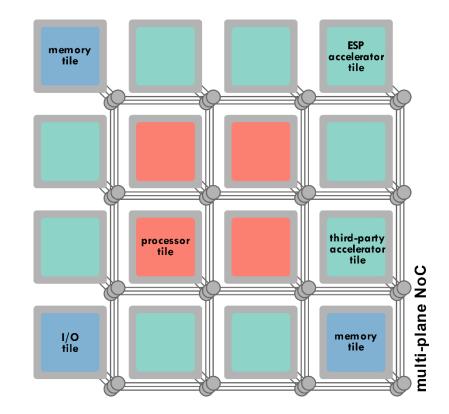

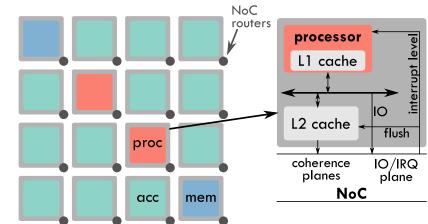

# **ESP** Architecture

- RISC-V Processors

- Many-Accelerator

- Distributed Memory

- Multi-Plane NoC

The ESP architecture implements a distributed system, which is scalable, modular and heterogeneous, giving processors and accelerators similar weight in the SoC

## **ESP Architecture: Processor Tile**

- Processor off-the-shelf

- RISC-V Ariane (64 bit)

SPARC V8 Leon3 (32 bit)

- $\circ$  L1 private cache

- L2 private cache

Configurable size

- $_{\circ}\,$  MESI protocol

- IO/IRQ channel

- $_{\circ}$  Un-cached

- Accelerator config. registers, interrupts, flush, UART, ...

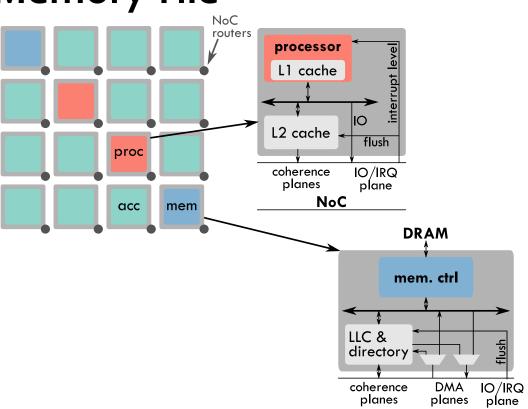

# **ESP Architecture: Memory Tile**

- External Memory Channel

- LLC and directory partition

- $_{\odot}$  Configurable size

- $_{\circ}$  Extended MESI protocol

- Supports coherent-DMA for accelerators

- DMA channels

- IO/IRQ channel

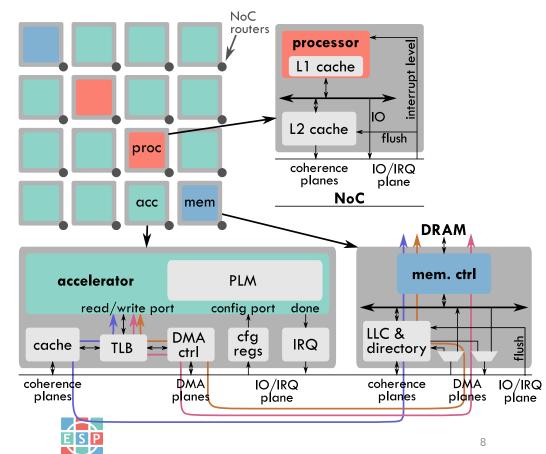

## **ESP Architecture: Accelerator Tile**

- Accelerator Socket w/ Platform Services

- Direct-memory-access

- Run-time selection of coherence model:

- Fully coherent

- LLC coherent

- Non coherent

- $_{\circ}$  User-defined registers

- $_{\odot}$  Distributed interrupt

IN THE CITY OF NEW YORK

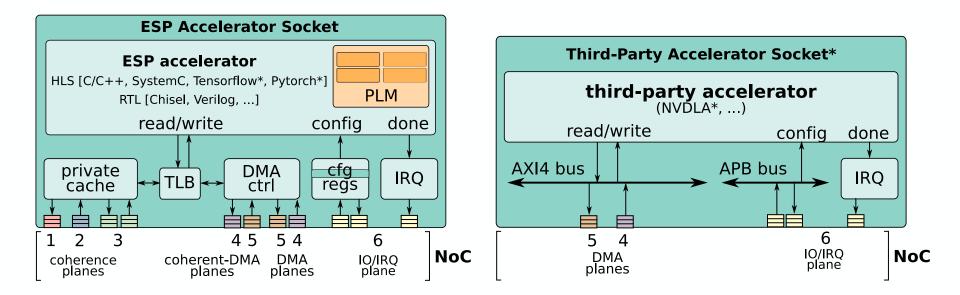

#### **ESP Accelerator Socket**

#### **ESP Platform Services**

| Accelerator tile<br>DMA<br>Reconfigurable coherence<br>Point-to-point<br>ESP or AXI interface<br>DVFS controller | Processor Tile<br>Coherence<br>I/O and un-cached memory<br>Distributed interrupts<br>DVFS controller |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Miscellaneous Tile<br>Debug interface                                                                            | Memory Tile<br>Independent DDR Channel                                                               |

| Performance counters access<br>Coherent DMA                                                                      | LLC Slice                                                                                            |

| Shared peripherals (UART, ETH,)                                                                                  | DMA Handler                                                                                          |

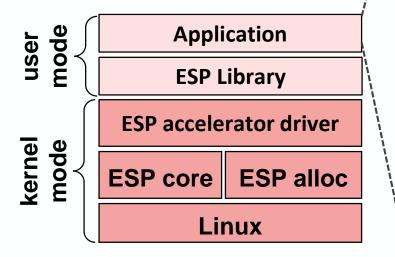

# **ESP Software Socket**

#### • ESP accelerator API

- Generation of device driver and unit-test application

- $_{\circ}\,$  Seamless shared memory

IN THE CITY OF NEW YORK

```

/*

* Example of existing C application

* with ESP accelerators that replace

* software kernels 2, 3 and 5

int *buffer = esp alloc(size);

for (...) {

kernel 1(buffer,...); /* existing software */

esp run(cfg k3);

kernel 4(buffer,...); /* existing software */

esp run(cfg k5);

/* existing checks

validate(buffer);

*/

*/

esp cleanup();

/* memory free

```

#### ESP

# The open-source heterogeneous system-on-chip platform

#### SystemC and C/C++ Accelerator Design Flow

## In Summary: ESP for Open-Source Hardware

- We contribute ESP to the OSH community in order to support the realization of

- more scalable architectures for SoCs that integrate

- more heterogeneous components, thanks to a

- more flexible design methodology, which accommodates different specification languages and design flows

- ESP was conceived as a heterogeneous integration platform from the start and tested through years of teaching at Columbia University

- We invite you to use ESP for your projects and to contribute to ESP!

https://www.esp.cs.columbia.edu

COLUMBIA UNIVERSITY

IN THE CITY OF NEW YORK

#### Thank you from the **ESP** team!

https://esp.cs.columbia.edu

https://github.com/sld-columbia/esp