### Zephyr and RISC-V: I Ain't Afraid Of No Ghosts

**FOSDEM 2024**

### THE SPEAKER

- Embedded Software Consultant

- Design Work

- Medical devices

- Scientific instruments

- LIDAR

- Custom ASIC

- Consumer electronics

- Experience/Expertise

- RTOS-based systems

- Embedded Linux/The Yocto Project

- Qt

cc 👔 🕥 CC BY-SA 4.0

#### Mohammed Billoo (mab@mab-labs.com)

/mab-embedded

💥 @mabembedded

### **THE SPEAKER**

### **BIOS FOOD Newsletter**

- Training/Workshops

- Virtual

- On-site/In-person

### www.mab-labs.com

### Agenda

- Background and motivation

- Process

- Issues Encountered

- Resolutions

- Enhancements

- Next Steps

- Q&A

### **BACKGROUND AND MOTIVATION**

### Background

- Embedded software

- Focus is on **software**

- Assume CPU does what you expect it to do

- Compiler is mature and well-defined

- Hardware is mature and well-defined\*

- » Mostly....

- » Errata

- Gets boring after > 10 years of doing "just software"

- Itch to understand how it works under the hood

### ISA

- Instruction Set Architecture

- Language to command a CPU

- Well-documented

CC BY-SA 4.0

- Nothing (technically) stopping you from:

- Building a CPU compliant to a particular ISA

- Costly + time consuming

- Issue (as always) comes from legal + financial

7

- Can get in trouble for violating IP

- ISA is considered vendor IP

### ISA

- How to (legally) use a proprietary ISA?

- Money (\$\$\$)

- Not friendly for hobbyists/individual

- Pay royalty to license ISA

- Pay fee for validated implementation

- Both

- More appropriate for (large) companies

- Pass added cost to (ultimately) consumer

# **RISC-V**

• A lot of buzz around an "open-source ISA"

#### • Free

- No license necessary to use the ISA

- No royalty or (significant) upfront cost

- Commercial advantage (for companies)

- Massive reduction in per unit cost

- (Hopefully) pass onto consumer

- Another advantage ... later

CC BY-SA 4.0

#### WCH Launches a Sub-10¢ RISC-V Microcontroller, While a \$6.90 Dev Board Gets You Started

Designed for less-computationally-demanding workloads, this 32-bit RISC-V chip is priced extremely aggressively.

Hackster.io

\$ 2 USD

# **RISC-V**

- Advantage for hobbyist?

- Yes!

- Can "implement" own RISC-V compliant CPU

- (Probably) easier to do than proprietary ISA

- Don't have to worry about paying royalty

- OK ...

- But how do I get started?

□ complication com/item?id=27607161

**Hacker News** new | past | comments | ask | show | jobs | submit

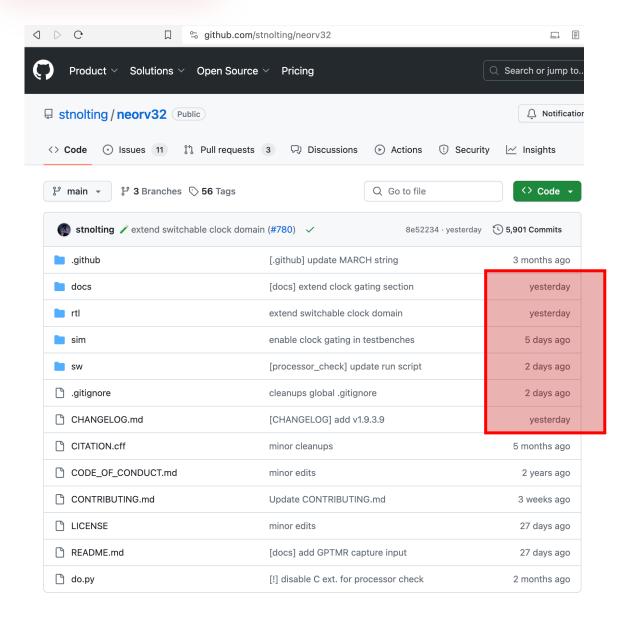

NEORV32: A customizable RISC-V SoC (adafruit.com)

73 points by \_quarks\_ on June 23, 2021 | hide | past | favorite | 10 comments

NEORV32: a customizable RISC-V SoC #RISCV #FPGA

The NEORV32 Processor is a customizable microcontroller-like system on chip (SoC) that is based on the RISC-V NEORV32 CPU. The project is intended as auxiliary processor in larger SoC designs or as *ready-to-go* stand-alone custom / customizable microcontroller.

CC BY-SA 4.0

###

#### [zephyr]\$ ls boards/riscv/

| adp_xc7k_ae350      | hifive1          | index.rst              | m2gl025_miv            | opentitan_earlgrey | sparkfun_red_v_things_plus |

|---------------------|------------------|------------------------|------------------------|--------------------|----------------------------|

| esp32c3_devkitm     | hifive1_revb     | <pre>it82xx2_evb</pre> | <pre>mpfs_icicle</pre> | qemu_riscv32       | stamp_c3                   |

| esp32c3_luatos_core | hifive_unleashed | <pre>it8xxx2_evb</pre> | neorv32                | qemu_riscv32e      | titanium_ti60_f225         |

| gd32vf103c_starter  | hifive_unmatched | litex_vexriscv         | niosv_g                | qemu_riscv64       | tlsr9518adk80d             |

| gd32vf103v_eval     | icev_wireless    | longan_nano            | niosv_m                | rv32m1_vega        | xiao_esp32c3               |

#### [zephyr]\$ ls soc/riscv/riscv-privileged/ andes\_v5 common gd32vf103 Kconfig.defconfig miv neorv32 opentitan starfive\_jh71xx virt CMakeLists.txt efinix-sapphire Kconfig Kconfig.soc mpfs niosv sifive-freedom telink\_b91

#### Interesting ....

### PROCESS

- Hardware?

- Neorv32 can be flashed to an FPGA

• 🕸 Exemplary setups and community projects targeting various FPGA boards and toolchains to get started.

- Have a list of FPGA boards that are supposed to work

- Decided to choose UPduino v3 board

- Lattice FPGA

**CC BY-SA 4.0**

- Inexpensive + small

- Available (at the time)

- Personally have Xilinx, Altera FPGA boards

- From past project work

- Why not use those?

- Not exact match to supported boards

- In (limited) experience, helps to have exact board

- Definitions in RTL may be different

- Pin definitions

- Clocks

- Result in weird/incorrect behavior

- Have FPGA, what next?

- Toolchain

- Decided to go with commercial toolchain (initially)

- Use vendor tools to get started

- Should\* work with FPGA

- Migrate to using open-source tools later

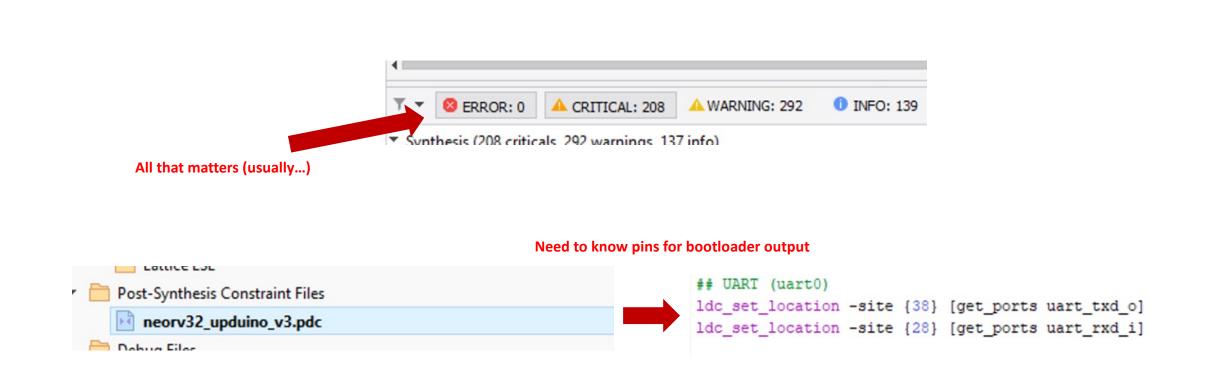

- First, had to jump through some hoops to get sources all aligned

- FPGA tools require some hand holding to get project to build

#### Usually

- Needed to run some pre-build steps

- Pre-build library

- But still ran into errors ...

### **Hunting Ghosts**

• Ran into initial errors

**CC BY-SA 4.0**

- Design not updated to support latest version of Radiant

- Attempted to resolve on my own

| project                                       | ank you for putting in the continued effort into this project. I just got involved in RISCV and this looks to be great<br>to get my feet wet. I'm working on a UPduino board using Lattice Semiconductor's Radiant toolchain. When I try to<br>ize the project, I get the following errors:                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Error<br>Error<br>Error                       | 2049990 Project ERROR <2049990> - D:/Documents/lattice/neorv32-setups/radiant/UPduino_v3/neorv32_d [<br>2049990 Project ERROR <2049990> - D:/Documents/lattice/neorv32-setups/radiant/UPduino_v3/neorv32_dmem.<br>2049990 Project ERROR <2049990> - D:/Documents/lattice/neorv32-setups/radiant/UPduino_v3/neorv32_dmem.                                                                                                                                                                                                                                                                                      |

| Review                                        | ng the neorv32_demem.ice40up_spram.vhd VHDL file, I don't see the definition of rden_1, addr_1, and wren_1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| siq<br>siq<br>siq<br>siq<br>siq<br>siq<br>siq | <pre>mal acc_en : std_ulogic;<br/>mal mem_cs : std_ulogic;<br/>mal rdat : std_ulogic;<br/>mal rdat : std_ulogic;<br/>SPRAM signals<br/>mal spram_dick : std_logic;<br/>mal spram_dick : std_logic_vector(13 downto 0);<br/>mal spram_dick : std_logic_vector(15 downto 0);<br/>mal spram_dick : std_logic_vector(15 downto 0);<br/>mal spram_do_lo : std_logic_vector(15 downto 0);</pre> |

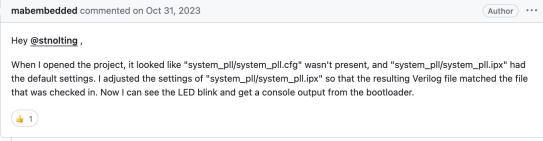

# **Hunting Ghosts**

- Maintainer responded with a fix in few days!

- Advantage of a (well-maintained) open-source project

- Still ran into an issue

CC BY-SA 4.0

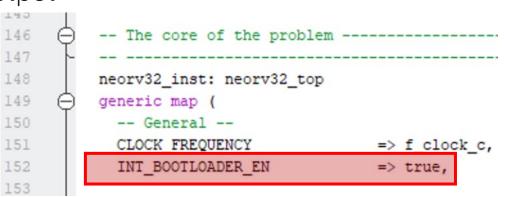

- Neorv32 has bootloader in RTL that can be enabled

- Flash application images to bootloader

- LED should blink for 10 seconds + UART output

- No blinky!

- No UART!

# **Hunting Ghosts**

• Toolchain issue!

CC BY-SA 4

- Expected (work long enough with FPGA people)

- Recently worked with an FPGA engineer to

- Debug IDE Segfault

- » Cost \$\$,000 license/year

- RE application binary

- » Located bug in how they used std library function

- » Worked around it ...

### Hello RISC-V World!

**CC BY-SA 4.0**

<< NEORV32 Bootloader >>

BLDV: Jul 28 2023 HWV: 0x01090004

CLK: 0x016e3600

MISA: 0x40901104

XISA: 0x00000093

SOC: 0x00bf800d

IMEM: 0x00010000

DMEM: 0x00010000

Autoboot in 8s. Press any key to abort. Aborted.

Available CMDs: h: Help

r: Restart

u: Upload

s: Store to flash

l: Load from flash

x: Boot from flash (XIP)

e: Execute

CMD:> Invalid CMD

CMD:>

Invalid CMD

CMD:>

cc 🛉 🛈 CC BY-SA 4.0

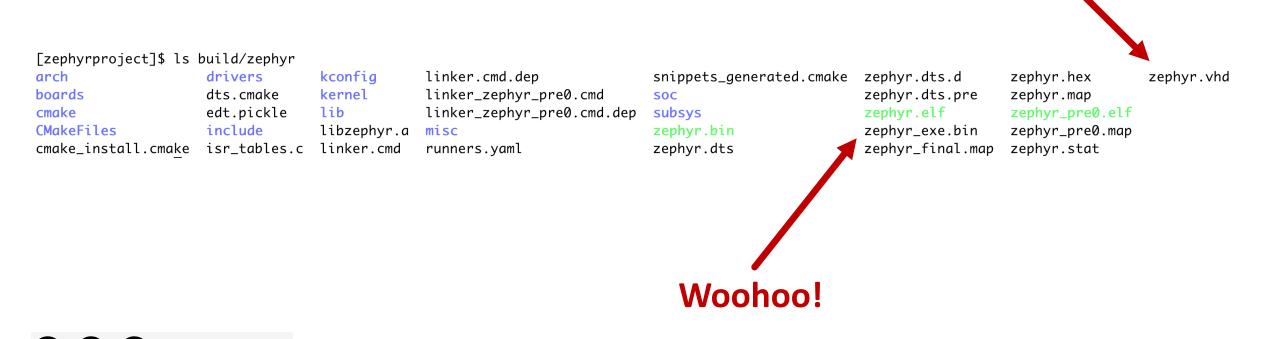

# Zephyr On RISC-V?

- west build -b neorv32 zephyr/samples/hello\_world ?

- Not sufficient

- Bootloader expects a bin file

- CONFIG\_BUILD\_OUTPUT\_BIN=y

- Add to prj.conf

- -- The ASM compiler identification is GNU

- -- Found assembler: /home/mab/mab\_home/zephyr-toolchains/zephyr-sdk-0.16.1/riscv64-zephyr-elf/

- -- The neorv32 image\_gen utility was not found, neorv32 image files cannot be generated

- -- Configuring done

### CC BY-SA 4.0

### Zephyr On RISC-V?

**CC BY-SA 4.0**

MAB LABS

image\_gen tool

Compile from Neorv32 repo under sw/

Add to PATH

### "zephyr.vhd"?

1 -- The NEORV32 RISC-V Processor: https://github.com/stnolting/neorv32

2 -- Auto-generated memory initialization file (for APPLICATION) from source file </media/mab/mab\_home/fosdem/zephyrproject/build/zephyr/zephyr.bin

```

>

3 -- Size: 17344 bytes

4 - MARCH: default

5 -- Built: 03.02.2024 04:28:31

6

7 -- prototype defined in 'neorv32_package.vhd'

8 package body neorv32_application_image is

9

10 constant application_init_image : mem32_t := (

11 x"80002197".

12 x"80818193",

13 x"00000297"

14 x"07c28293"

15 x"30529073".

16 x"0000a011".

17 x"00000037".

18 x"30001073"

19 x"30401073"

20 x"907355f5"

21 x"10733205"

22 x"1073b000",

23 x"1073b800",

```

### **Can embed our application inside FPGA memory!**

CC BY-SA 4.0

**RTL**!

stnolting on Dec 9, 2023 Maintainer

Sorry for the late reply...

There is a (work-in-progress) PR to update the Zephyr port according to the processor's new memory layout: <a href="mailto:zephyr#65627">zephyr#65627</a>

- No output to console

- Problem when working with FPGAs/hardware

- If hardware changes underneath, software has to follow

- Used a forked version of Zephyr with fixes

- Actually compiles

- Does it work?

cc 👔 🕥 CC BY-SA 4.0

[fosdem]\$ ./uart\_upload.sh /dev/ttyUSB0 zephyrproject/build\_neorv32/zephyr/zephyr\_exe.bin

Uploading. Done.

Included in neorv32 repo to upload binary to bootloader

**CC BY-SA 4.0**

nvalid CMD

CMD:> h

Available CMDs:

h: Help

r: Restart

u: Upload

s: Store to flash

l: Load from flash

x: Boot from flash (XIP)

e: Execute

CMD:> e

Booting from 0x0000000...

\*\*\* Booting Zephyr OS build 6f56a6a91e2c \*\*\*

Hello World! neorv32

#### Woohoo!

- (Personally) most interesting feature in RISC-V

- ISA Extension to allow for operations optimized in hardware

- Call from SW using compiler intrinsic

| tart Page X   | Reports          | ×  | 📝 neorv    | 32_u | pduino_v3_top.vhd ×    |

|---------------|------------------|----|------------|------|------------------------|

| The core o    | of the problem   |    |            |      |                        |

| neorv32_inst: | neorv32_top      |    |            |      |                        |

| ) generic map | (                |    |            |      |                        |

| General       |                  |    |            |      |                        |

| CLOCK_FREQU   | JENCY            | => | f_clock_c, |      | clock frequency of clk |

| INT_BOOTLOF   | ADER_EN          | => | true,      |      | boot configuration: tr |

| RISC-V (      | CPU Extensions   |    |            |      |                        |

| CPU_EXTENSI   | ION_RISCV_C      | => | true,      |      | implement compressed e |

| CPU_EXTENSI   | ION_RISCV_M      | => | true,      |      | implement mul/div exte |

| CPU_EXTENSI   | ION_RISCV_U      | => | true,      |      | implement user mode ex |

| CPU_EXTENSI   | ION_RISCV_Zicntr | => | true,      |      | implement base counter |

| CPU_EXTENSI   | ION_RISCV_Zxcfu  | => | true,      |      | add CFU support        |

|               |                  |    |            |      |                        |

| Internal      | ory -            | -  |            |      |                        |

| MEM_INT_IME   | EM_EN            | => | true,      |      | implement processor-in |

| MEM_INT_IME   | EM_SIZE          | => | 64*1024,   |      | size of processor-inte |

|               |                  |    |            | _    |                        |

**CC BY-SA 4.0**

• Hardware multiply and add!

| Iterative Multiply-Add Unit                    |                                           |                             |   |

|------------------------------------------------|-------------------------------------------|-----------------------------|---|

|                                                |                                           |                             | - |

| iteration control                              |                                           |                             |   |

| <pre>madd_control: process(rstn_i, clk_:</pre> | L)                                        |                             |   |

| begin                                          |                                           |                             |   |

| if (rstn_i = '0') then                         |                                           |                             |   |

| <pre>madd.sreg &lt;= (others =&gt; '0');</pre> |                                           |                             |   |

| <pre>elsif rising_edge(clk_i) then</pre>       |                                           |                             |   |

| operation trigger                              |                                           |                             |   |

| if (control.busy = '0') and                    |                                           | -                           |   |

| _                                              | is actually triggered by a cu             |                             |   |

|                                                | and this is a R4-type inst                |                             |   |

|                                                | = "00") then trigger only                 | for specific funct3 values  |   |

| <pre>madd.sreg(0) &lt;= '1';</pre>             |                                           |                             |   |

| else                                           |                                           |                             |   |

| <pre>madd.sreg(0) &lt;= '0';</pre>             |                                           |                             |   |

| end if;                                        |                                           |                             |   |

| simple shift register for the                  |                                           |                             |   |

| madd.sreg(madd.sreg'left downto                | <pre>1) &lt;= madd.sreg(madd.sreg'l</pre> | eft-1 downto 0); shift left |   |

| end if;                                        |                                           |                             |   |

| end process madd_control;                      |                                           |                             |   |

| processing has reached last stat               | ge (= done) when sreg's MSB is            | s set                       |   |

| nadd.done <= madd.sreg(madd.sreg'le            |                                           |                             |   |

30

- Doesn't build for UPduino board

- Logic doesn't fit

- (Another) typical problem with FPGA designs

- Resource (and timing) constraints

8 51001122 ERROR - Design doesn't fit into device specified, refer to the design summary section for more details.

- From SW?

- Neorv32 "sw" directory has relevant functions

- Detect if CFU is enabled

- Call appropriate CFU

[sw]\$ cd example/ atomic\_test/ bus\_explorer/ coremark/ demo\_blink\_led/ demo\_blink\_led\_asm/ demo\_cfs/ demo\_cfu/ demo\_mtime/

demo\_crc/ demo\_neopixel/

demo\_dma/ demo\_newlib/

demo\_emulate\_unaligned/ demo\_onewire/

demo\_gptmr/ demo\_pwm/

demo\_hpm/ demo\_sdi/

CC 👔 🕥 CC BY-SA 4.0

- 96 // check if the CFU is implemented at all (the CFU is wrapped in the core's "Zxcfu" ISA extension)

- 97 if (neorv32\_cpu\_cfu\_available() == 0) {

- 98 neorv32\_uart0\_printf("ERROR! CFU ('Zxcfu' ISA extensions) not implemented!\n");

- 99 return 1;

```

109 /*

110

The CFU custom instructions can be used as plain C functions as they are simple "intrinsics".

111

There are 4 "prototype primitives" for the CFU instructions (define in sw/lib/include/neorv32_cfu.h):

112

113

> neorv32_cfu_r3_instr(funct7, funct3, rs1, rs2) - for r3-type instructions (custom-0 opcode)

114

> neorv32_cfu_r4_instr(funct3, rs1, rs2, rs3)

- for r4-type instructions (custom-1 opcode)

115

- for r5-type instruction A (custom-2 opcode)

> neorv32_cfu_r5_instr_a(rs1, rs2, rs3, rs4)

116

117

> neorv32_cfu_r5_instr_b(rs1, rs2, rs3, rs4)

- for r5-type instruction B (custom-3 opcode)

```

```

136 for (i=0; i<TESTCASES; i++) {</pre>

```

137 rs1 = xorshift32();

```

138 neorv32_uart0_printf("%u: neorv32_cfu_r3_instr( funct7=0b1111111, funct3=0b000, [rs1]=0x%x, [rs2]=0x%x ) = ", i, rs1, 0);

139 // here we are setting the funct7 bit-field to all-one; however, this is not used at all by the default CFU hardware module.

140 neorv32_uart0_printf("0x%x\n", neorv32_cfu_r3_instr(0b111111, 0b000, rs1, 0));

```

141 }

# **Next Steps: CFU In Zephyr?**

- Didn't see existing support for using Neorv32 CFU in Zephyr

- Maybe pull in is as external module via West

- Add it to Zephyr?

### **Summary and Next Steps**

- UPduino running Neorv32 works with Zephyr!

- Need to use forked version

- Help get PR past the finish line

- Some comments need addressing

- Can help address those comments and get mainlined

- Get bigger FPGA for CFU support

C BY-SA 4.0

• Determine appropriate strategy to add CFU support in Zephyr

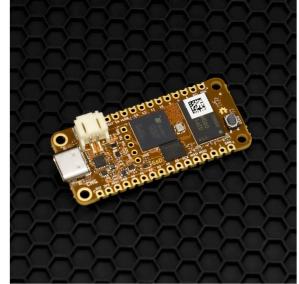

#### OrangeCrab

The OrangeCrab is a feather form factor electronics development board. For the Lattice ECP5 FPGA. The board follows the slim feather board specification from Adafruit. The FPGA is compatible with all open source toolchains and is perfect for experimenting with RISC-V cores. There aren't many FPGA boards available that make use of the ECP5, but here are some distinct features that set this board apart:

- Small Compact size (Take it anywhere!)

- Direct USB connection to the FPGA (Operate as a DFU, MSC, CDC, or composite device!)

- On-board DDR3 Memory (1Gbit!)

- Pre-loaded DFU bootloader (No external programmer required!)

- It's Orange!

The current hardware version that we are shipping is V0.2.1.

# Thank you!

### **Questions?**

**FOSDEM 2024**